# **Engineering of Semiconductor**

:Semiconductor Physics and Devices

## Chapter 2. Silicon Technology

Applied Nanomaterials & Devices LAB. Electronics & Probes by Materials Engineering

## Objectives

Overview of Silicon Technology

- Wafer preparation

- Oxidation

- Lithography

- Etching

- Doping

- Deposition

- Packaging

| Steps to Obtaining Semiconductor Grade Silicon (SGS) |                                                                                                                                  |                                                                                    |  |  |  |  |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|

| Step                                                 | <b>Description of Process</b>                                                                                                    | Reaction                                                                           |  |  |  |  |

| 1                                                    | Produce metallurgical grade<br>silicon (MGS) by heating sil<br>ica with carbon                                                   | SiC (s) + SiO <sub>2</sub> (s) $\rightarrow$ Si (l) + SiO(g) + CO (g)              |  |  |  |  |

| 2                                                    | Purify MG silicon through a<br>chemical reaction to produce<br>a silicon-bearing gas of<br>trichlorosilane (SiHCl <sub>3</sub> ) | Si (s) + 3HCl (g) $\rightarrow$ SiHCl <sub>3</sub> (g) + H <sub>2</sub> (g) + heat |  |  |  |  |

| 3                                                    | SiHCl <sub>3</sub> and hydrogen react in<br>a process called Siemens to<br>obtain pure semiconductor-<br>grade silicon (SGS)     | $2SiHCl_3(g) + 2H_2(g) \rightarrow 2Si(s) + 6HCl(g)$                               |  |  |  |  |

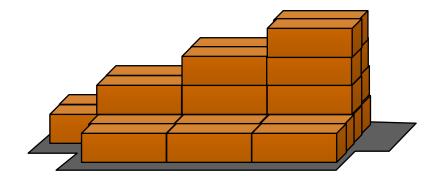

#### Atomic Order of a Crystal vs. Amorphous Structure

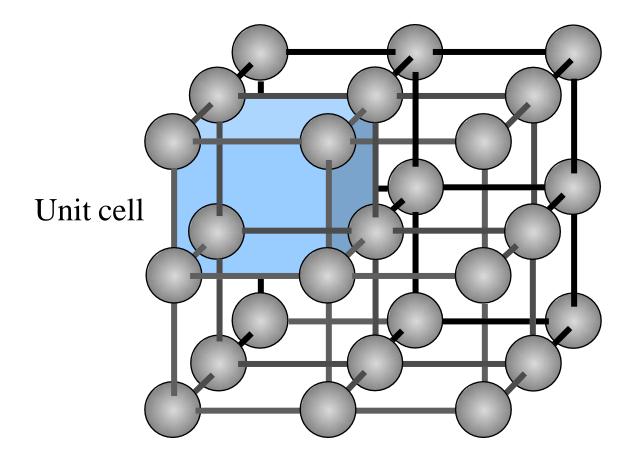

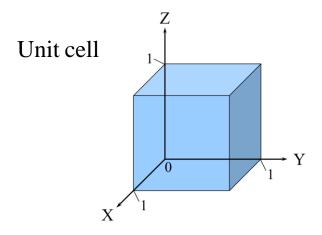

#### Unit Cell in 3-D Structure

the smallest portion of a crystal lattice that shows the three-dimensional pattern of the entire crystal

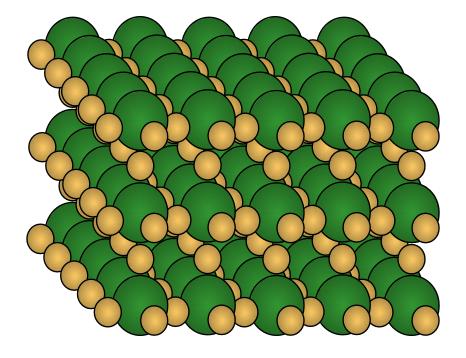

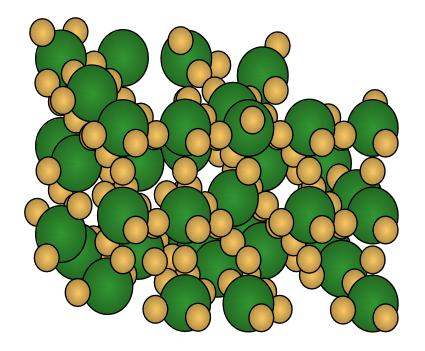

Polycrystalline and Monocrystalline Structures

Faced-centered Cubic (FCC) Unit Cell

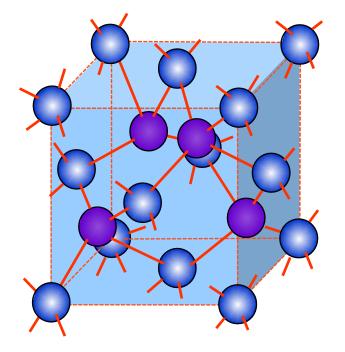

Silicon Unit Cell: FCC Diamond Structure

#### Crystalline structure of Silicon

Polycrystalline structure

Monocrystalline structure

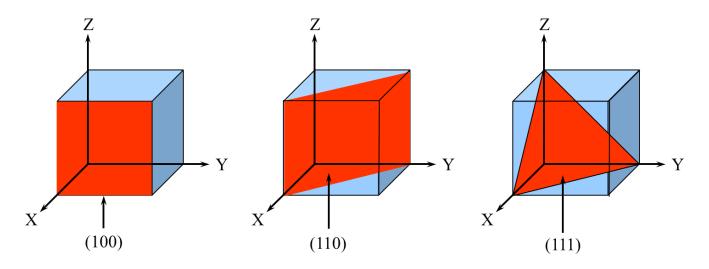

#### Axes of Orientation for Unit Cells

Miller indices form a notation system in <u>crystallography</u> for planes in <u>crystal (Bravais) lattices</u>

Homework "Miller Index"

#### Miller Indices of Crystal Planes

Growth of singlecrystal Silicon

- CZ Method

- CZ Crystal Puller

- Doping

- Impurity Control

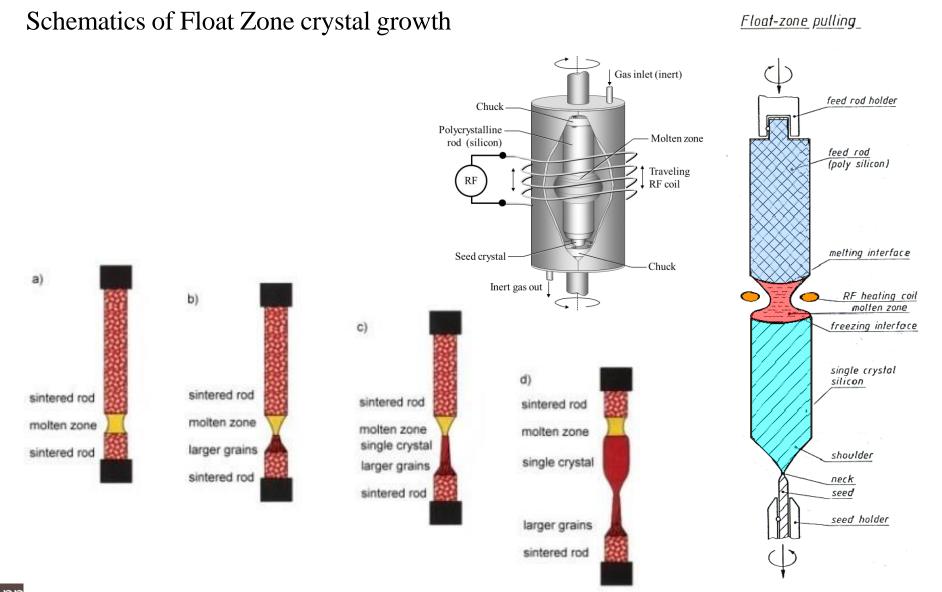

- Float-Zone Method

- Reasons for Larger Ingot Diameters

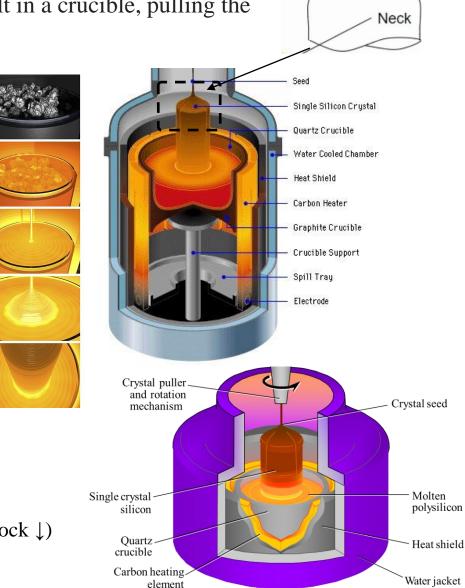

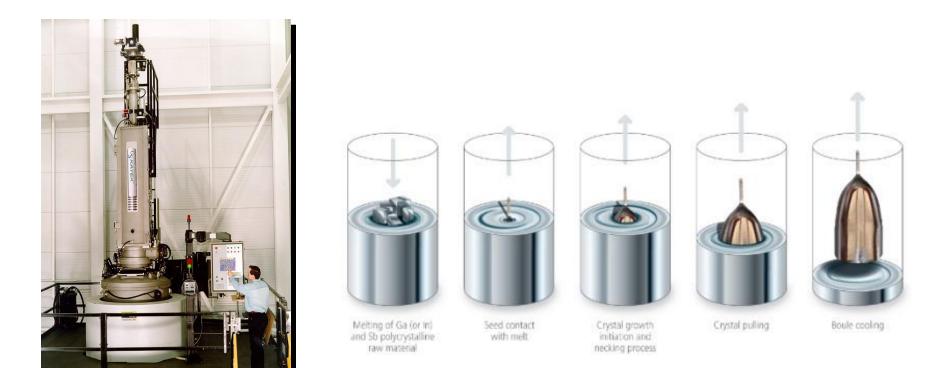

The Czochralski (CZ) method is a crystal growth technology that starts with insertion of a small seed crystal into a melt in a crucible, pulling the seed upwards to obtain a single crystal.

- In 1918, Czochralski developed process.

- Polycrystal Si  $\rightarrow$  single crystal Si

- Single crystal is pulled from a melt.

- Orientation of seed determine the orientation of Si wafer.

#### [Process]

- Melting of P-Si in quartz crucible

- Deep the crystal seed in to the Si melt

\*Crystal growth at the interface of melt following the crystallographic structure of seed

- Seed rotation + pulled-up from the melt fast speed (necking, defect ↓)

→ slow speed (shoulder, diameter ↑)

- Growth (Ingot)

- Increase pull speed (ingot diameter & thermal shock  $\downarrow$ )

Shoulder

#### CZ Crystal Puller

Photograph courtesy of Kayex Corp., 300 mm Si crystal puller

https://www.youtube.com/watch?v=2qLI-NYdLy8&t=141s

#### Dopant Concentration Nomenclature

|             |                  |                                            | Concentration (Atoms/cm <sup>3</sup> ) |                                                 |                                      |  |

|-------------|------------------|--------------------------------------------|----------------------------------------|-------------------------------------------------|--------------------------------------|--|

| Dopant      | Material<br>Type | < 10 <sup>14</sup><br>(Very Lightly Doped) | $10^{14}$ to $10^{16}$ (Lightly Doped) | 10 <sup>16</sup> to 10 <sup>19</sup><br>(Doped) | >10 <sup>19</sup><br>(Heavily Doped) |  |

| Pentavalent | n                | n <sup></sup>                              | n                                      | n                                               | n <sup>+</sup>                       |  |

| Trivalent   | р                | p                                          | p                                      | р                                               | $p^+$                                |  |

#### Float Zone Crystal Growth method

Applied Nonomaterials & Devices LAB. Electronics & Probes by Materials Engineering

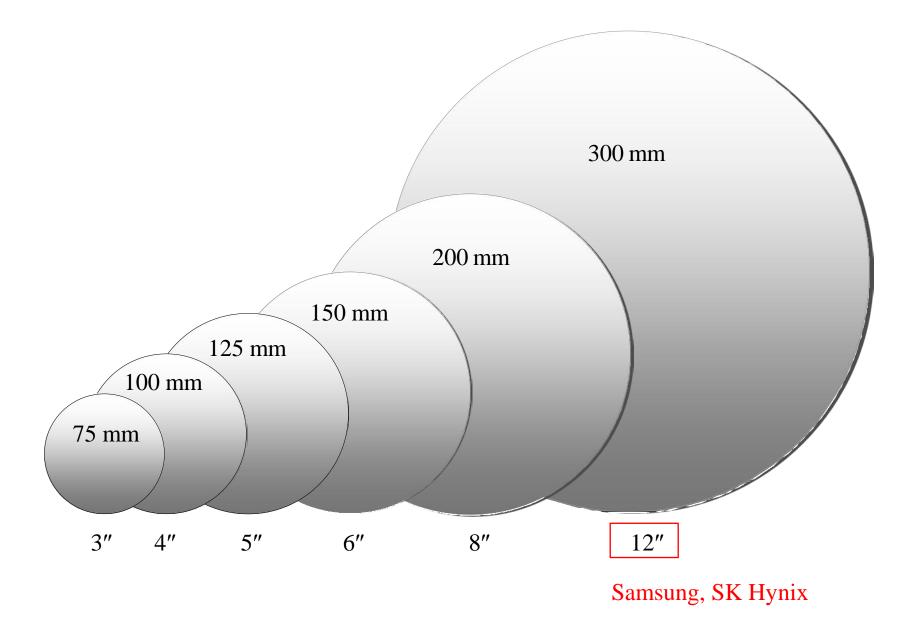

#### Wafer Diameter Trends for Silicon

Applied Nanomaterials & Devices LAB. Electronics & Probes by Materials Engineering

#### Why larger wafer?

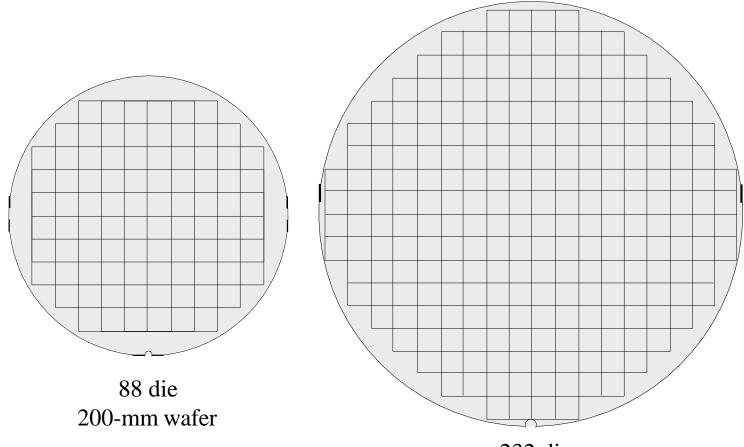

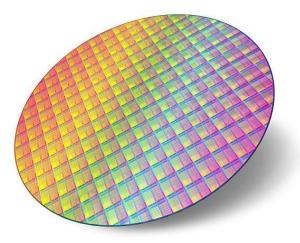

Increase in Number of Chips on Larger Wafer Diameter

232 die 300-mm wafer

## Crystal Defects in Silicon

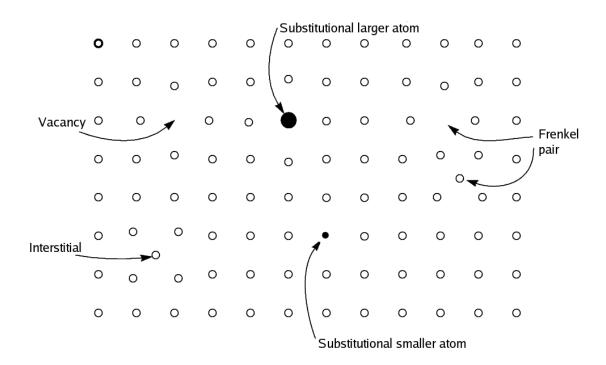

A crystal defect (*microdefect*) is any interruption in the repetitive nature of the unit cell crystal structure.

Three general types of crystal defects in silicon:

- 1. Point defects: Localized crystal defect at the atomic level

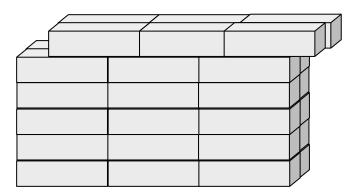

- 2. Dislocations: Displaced unit cells

### Crystal Defects in Silicon

#### Point defects

Point defects are defects that occur only at or around a single lattice point

Vacancy defects are lattice sites which would be occupied in a perfect crystal, but are vacant Interstitial defects are atoms that occupy a site in the crystal structure at which there is usually not an atom

Frenkel defect: A nearby pair of a vacancy and an interstitial

## Crystal Defects in Silicon

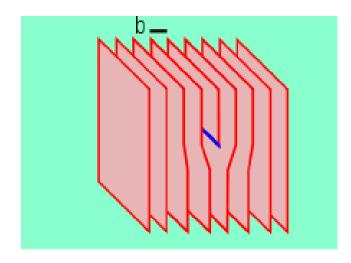

Dislocations

<u>Dislocations</u> are linear defects, around which the atoms of the crystal lattice are misaligned

#### Dislocations in Unit Cells

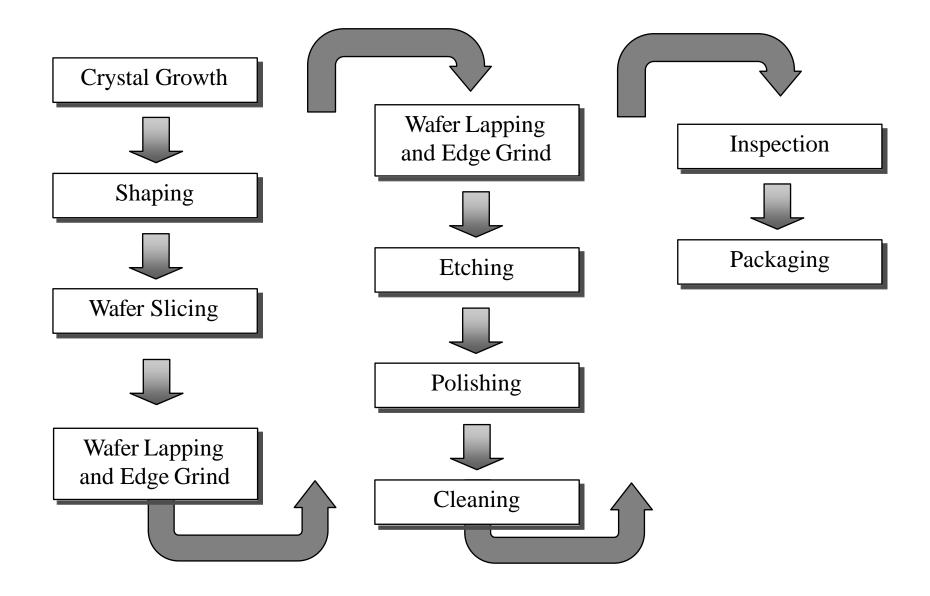

#### **Basic Process Steps for Wafer Preparation**

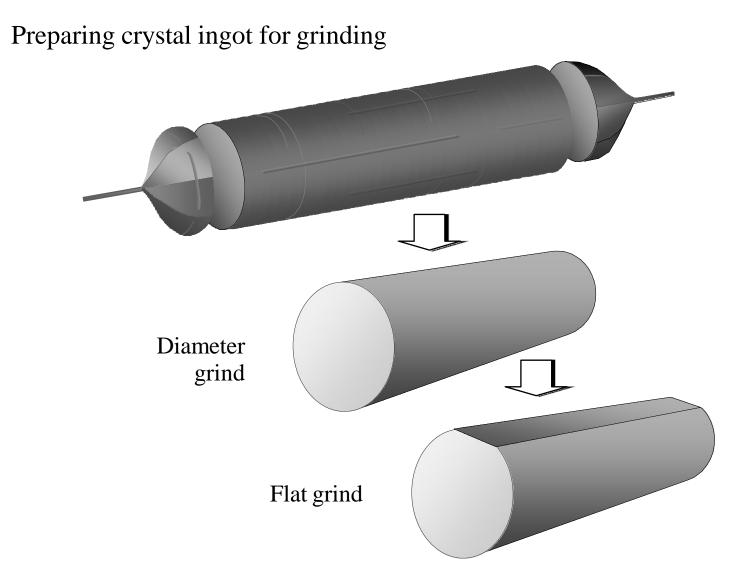

#### Ingot Diameter Grind

Applied Nanomaterials & Devices LAB. Electronics & Probes by Materials Engineering

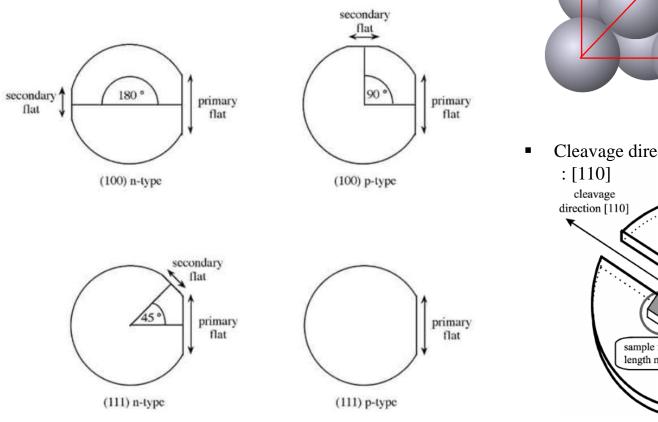

#### Wafer Identifying Flats

#### Silicon wafer

-Round-shaped + flat -Size : 2in, 4in, 6in, 8in ~ 18in - Type : <100>,<110>,<111>

[110] [100] Cleavage direction wafer front side (100)sample for DZ determination cross section (111)sample for diffusion length measurement

|                                                                                                                 |                          | TRADUCTOR -                                                   |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------|--|--|--|

|                                                                                                                 | QL Polished Wafer(PRIME) |                                                               |  |  |  |

| Station and Station                                                                                             | SPEC NUMBER: /           | GROWTH METHOD: CZ                                             |  |  |  |

|                                                                                                                 | ORIENTATION: <100> 0°±1° | THICKNESS: 675±25um                                           |  |  |  |

|                                                                                                                 | TYPE/DOPANT: P/B         | DIAMETER:      150.0±0.2mm        PACKING DATE:      20/11/14 |  |  |  |

|                                                                                                                 | RESISTIVITY: <0.005 Ω.cm | (7Q)QUANTITY: 25                                              |  |  |  |

|                                                                                                                 | (P)PART NUMBER: /        |                                                               |  |  |  |

|                                                                                                                 |                          | (1V)VENDER: QL                                                |  |  |  |

|                                                                                                                 | (1T)LOT#: 6BL05GZ0       |                                                               |  |  |  |

|                                                                                                                 |                          |                                                               |  |  |  |

| Carl Carl                                                                                                       | BACK SURFACE:            |                                                               |  |  |  |

|                                                                                                                 |                          |                                                               |  |  |  |

|                                                                                                                 | SN 6BL05GZ0-1            | 25                                                            |  |  |  |

| California a la california de la california | 08203020-1               |                                                               |  |  |  |

|                                                                                                                 |                          |                                                               |  |  |  |

| Service and and                                                                                                 |                          |                                                               |  |  |  |

|                                                                                                                 |                          |                                                               |  |  |  |

|                                                                                                                 |                          |                                                               |  |  |  |

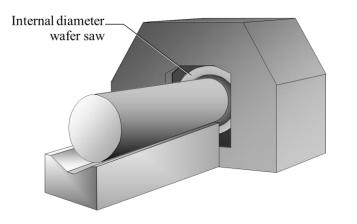

## Wafer preparation

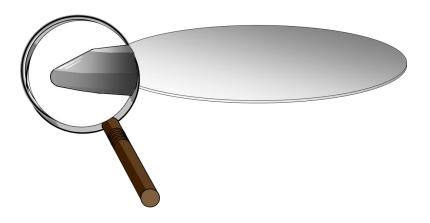

Internal Diameter Saw

#### Polished Wafer Edge

# Chemical Etch of Wafer Surface to Remove Damage

Applied Nanomaterials & Devices LAB. Electronics & Probes by Materials Engineering

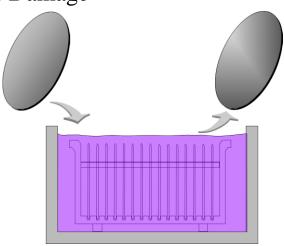

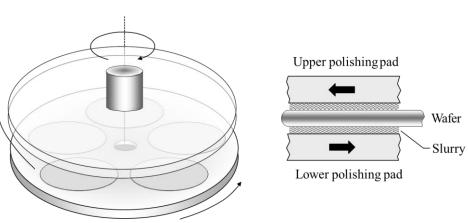

Double-Sided Wafer Polish

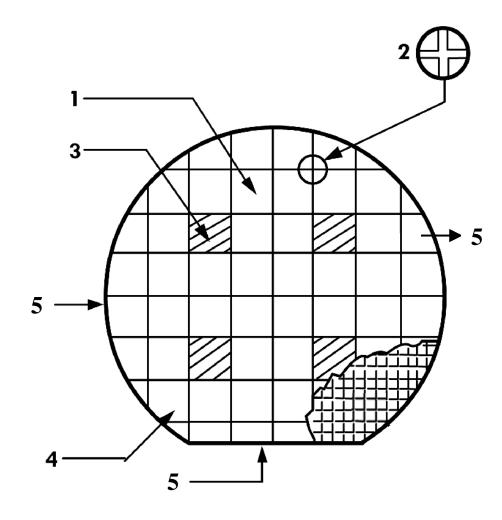

## **Terminology of wafer**

- 1. Chip, Die, Device

- 2. Scribe line

- 3. Test element group (TEG)

- 4. Edge die

- 5. Flat zone

## Yield

- Opposite of defective rate

- Output / Input

- Division of Yield

- : 4 Group Fabrication, Probe, Package, Test

- Total Yield (CUM Yield) : ( $Y_{fab.}$ ) x ( $Y_{prove}$ ) x ( $Y_{package}$ ) x ( $Y_{test}$ )

## Wafer processing

Classification of wafer processing

| Class                   | Purpose                                     | Technique.                                                                                                              |  |

|-------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| Thin film<br>deposition | Formation of thin film<br>on wafer          | Oxidation : atmospheric pressure<br>CVD : epitaxy, plasma assist<br>Deposition : Metal<br>Sputtering : Metal, insulator |  |

| Patterning              | Selective<br>deposition/etching<br>on wafer | Photolithography<br>Photoresist, exposure, develop<br>Etching : Wet, Dry (plasma, ion)                                  |  |

| Doping                  | Electrical property control<br>Of wafer     | Thermal diffusion<br>Implantation                                                                                       |  |

# End of Slide

Applied Nanomaterials & Devices LAB. Electronics & Probes by Materials Engineering